APPLICATION NOTES

# z8751 VSG DIO

# Contents

| Port Description           | 2 | Pinout                                  | 5  |

|----------------------------|---|-----------------------------------------|----|

| Block Diagram              | 3 | MIPI Functionality                      | 5  |

| Digital Input/Output (DIO) | 4 | Accessories: Mating Connectors & Cables | 5  |

| General Specifications     | 4 | Applications                            | 6  |

| DIO Clock Rates            | 4 | DIO Output Commands                     | 7  |

|                            |   | MIPI Command Sequencing Example         | 10 |

# Port Descriptions

#### Front Panel

| Label     | Туре                            | Description                                                       |

|-----------|---------------------------------|-------------------------------------------------------------------|

| I OUT +,- | SMA                             | Differential baseband I output                                    |

| Q OUT +,- | SMA                             | Differential baseband Q output                                    |

| EXT IN    | SMB                             | External input for trigger or reference                           |

| EXT OUT   | SMB                             | External output for trigger, reference or event                   |

| RF output | SMA                             | RF output                                                         |

| LO IN     | SMA                             | Local oscillator input                                            |

| DIO       | Header, 8-pin,<br>0.05" spacing | Digital input/output, 4-signal (e.g. MIPI, SPI, I <sup>2</sup> C) |

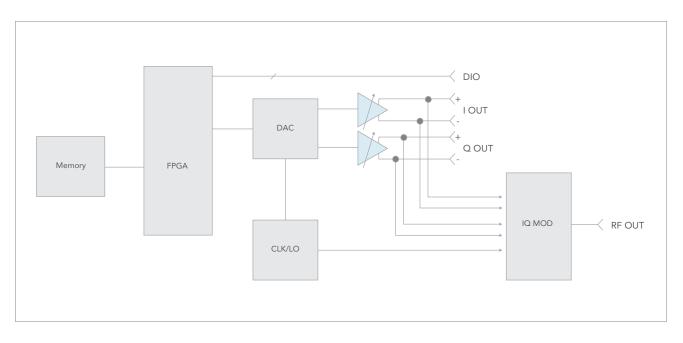

# Block Diagram

# Digital Input/Output (DIO)<sup>1</sup>

## **General Specifications**

| Specification                   | Value                                                                                                               |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Functionality                   | 4-bit bi-directional Digital I/O software programmable. Supports serial interfaces such as MIPI, SPI, I2C, etc.     |

| Programmable Clock Rate         | Up to 125 MHz                                                                                                       |

| Programmable Logic              | $\geq$ 8 ns resolution                                                                                              |

| Programmable Direction          | Input (52 kΩ pull-down) or Output                                                                                   |

| Programmable Source/Destination | Backplane triggers, external in/out, trigger event                                                                  |

| Output Level                    | Programmable Level:<br>Default: +1.2V into open load<br>Range: +1.2V to +3.6V into open load<br>Level accuracy: ±5% |

| Output Drive                    | $\geq \pm 3 \text{ mA } @ 1.2V$<br>$\geq \pm 8 \text{ mA } @ 1.8V$<br>$\geq \pm 12 \text{ mA } @ 3.6V$              |

| Output Enable                   | Tri-State Output Capability                                                                                         |

| Connector                       | Latching Header, 8-pin, 0.05" spacing<br>4 DIO signals with ground pairs                                            |

#### **DIO Clock Rates**

| Divider       | Sample Clock | MIPI Clock  | REF Clock   | SSBI Clock |

|---------------|--------------|-------------|-------------|------------|

| 1 (no divide) | 125 MHz      | 104 MHz     | 100 MHz     | 38.4 MHz   |

| 2             | 62.5 MHz     | 52 MHz      | 50 MHz      | 19.2 MHz   |

| 4             | 31.25 MHz    | 26 MHz      | 25 MHz      | 9.6 MHz    |

| 6             | 20.833 MHz   | 17.333 MHz  | 16. 666 MHz | 6.4 MHz    |

| 8             | 15.625 MHz   | 13 MHz      | 12.5 MHz    | 4.8 MHz    |

| 10            | 12.5 MHz     | 10.4 MHz    | 10 MHz      | 3.84 MHz   |

| 12            | 10.4166 MHz  | 8.666 MHz   | 8.333 MHz   | 3.2 MHz    |

|               |              |             |             |            |

| 510           | 245.098 kHz  | 203.921 kHz | 196.078 kHz | 75.294 kHz |

#### Pinout

| Pin Number | Signal | Pin Number | Signal |

|------------|--------|------------|--------|

| 1          | GND    | 2          | DIOO   |

| 3          | GND    | 4          | DIO1   |

| 5          | GND    | 6          | DIO2   |

| 7          | GND    | 8          | DIO3   |

### **MIPI** Functionality

| Feature                | Details                                                                                                                                                                             |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transactions Supported | Write register 0<br>Write register<br>Read Register<br>Write Extended<br>Read Extended<br>Write Long<br>Read Long                                                                   |

| Sequences              | Up to 4 serial data stream sequences<br>Max of 32 RD/WR MIPI byte transactions per sequence,<br>Multi-sequence capture capable,<br>Single transaction pre/post a burst transactions |

| Triggering             | Independent triggers per data stream, armed by previous sequence completion                                                                                                         |

| Buffer Update          | Ability to update one buffer while playing other buffer (ping/pong)                                                                                                                 |

### Accessories: Mating Connectors & Cables

| Part                                                         | Part Number                                       |

|--------------------------------------------------------------|---------------------------------------------------|

| Mating Header Connector<br>(requires own cable)              | 3M, 45108-010030<br>Strain relief: 3M, 3448-45108 |

| 6" Mating Cable with header connector                        | LitePoint, 0150-ZDIO-002                          |

| 12" Mating Cable with header connector                       | LitePoint, 0150-ZDIO-003                          |

| 24" Mating Cable with header connector                       | LitePoint, 0150-ZDIO-004                          |

| 24" Mating Cable with header connector<br>and Breakout Board | LitePoint, 0150-ZDIO-001                          |

# Applications

The LitePoint z8751 Vector Signal Generator is suitable for WLAN 802.11 a/b/g/j/n/p/ac/af/ah/ax, Cellular 2G/3G/4G, Bluetooth and ZigBee standards. The z8751 provides RF and baseband I/Q signal outputs corresponding to vector modulated signals. In addition, a DIO connector adds serial interfaces such as MIPI, SPI and I<sup>2</sup>C that can be time synchronized to the RF signal.

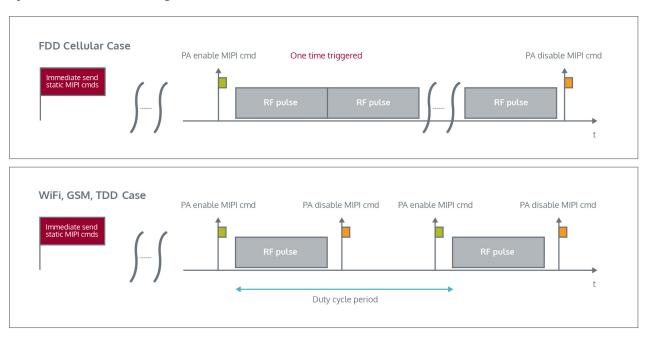

MIPI-RFFE testing is a specific application for the DIO connector. Preloaded MIPI patterns are generated in a sequence that is time aligned with the RF output signal. This is necessary for PA/FEM testing where the device is enabled/disabled using a MIPI command that must be accurately time-aligned with the RF burst.

### Synchronized MIPI testing

Synchronized MIPI testing is a challenging procedure. The time gap between the MIPI command and the RF pulse should be almost negligible. The DIO connector and the RF signal synchronize automatically through the same FPGA. The auto synchronization is successful with burst and modulated RF signals.

SPI is a serial interface method designed for short distance communication. PA/FEM components with SPI capabilities exchange synchronized data with a master device (z8751). The SPI packet determines mode and state of PA/FEM components.

The DIO connector also configures General Purpose Input/output (GPIO) functionalities. GPIO pins are unused by default, but can be configured as input or output depending on the testing scenario. During testing GPIO pins set input/output modes on chipsets, external electronics, switches, etc.

#### DIO Output Commands

| Command                 | Parameter Form                                     | Response                | Notes                                                                                                                                              |

|-------------------------|----------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| :DIO:CLOCk              | <frequency></frequency>                            |                         | DIO BB Only, <frequency hz="" in=""></frequency>                                                                                                   |

| :DIO:CLOCk?             |                                                    | <frequency></frequency> |                                                                                                                                                    |

| :DIO <n>:DATA</n>       | <1 0>                                              |                         | $ = 0-3$ DIO pin selection (PXIe_DIO only)                                                                                                         |

| :DIO <n>:DATA?</n>      |                                                    | <1 0>                   | <n> = 0-3 DIO pin selection.<br/>Reads back configured output data.<br/>See sense command for read data.<br/>(PXIe_DIO only)</n>                   |

| :DIO <n>:DIRection</n>  | <in out></in out>                                  |                         | $ = 0-3$ DIO pin selection. (PXIe_DIO only)                                                                                                        |

| :DIO <n>:DIRection?</n> |                                                    | <in out></in out>       | $ = 0-3$ DIO pin selection. (PXIe_DIO only)                                                                                                        |

| :DIO:ENABle             | <0N 0FF,1 0>                                       |                         | Global Enable (PXIe_DIO only)                                                                                                                      |

| :DIO:ENABle?            |                                                    | <1 0>                   | Query global enable (PXIe_DIO only)                                                                                                                |

| :DIO:LEVel              | <voltage></voltage>                                |                         | Voltage is floating point < 3.6V<br>(PXIe_DIO only)                                                                                                |

| :DIO:LEVel?             |                                                    | <voltage></voltage>     | Floating point (PXIe_DIO only)                                                                                                                     |

| :DIO:RESet              |                                                    |                         | Resets SDS to Defaults/Legacy                                                                                                                      |

| :DIO:SEQuence:BURSt     | <0N 0FF,1 0>                                       |                         | 1=Burst (single-shot), 0 = continuous                                                                                                              |

| :DIO:SEQuence:BURSt?    |                                                    | <0N 0FF,1 0>            | 1=Burst (single-shot), 0 = continuous                                                                                                              |

| :DIO:SEQuence:CLEar     | <sequence_id></sequence_id>                        |                         | Clears sequence of commands.                                                                                                                       |

| :DIO:SEQuence:DELay     | <sequence_id>,<br/><cycles></cycles></sequence_id> |                         | <sequence_id> specifies the SDS command<br/>buffer<br/><cycles> sets the number of clock cycles<br/>(periods) to delay</cycles></sequence_id>      |

| :DIO:SEQuence:DELay?    | <sequence_id>,</sequence_id>                       | <cycles></cycles>       | <sequence_id> specifies the SDS command<br/>buffer<br/><cycles> returns the currently configured<br/>number of delay cycles</cycles></sequence_id> |

| :DIO:SEQuence:GAP       | <gap></gap>                                        |                         | <gap> sets the number of extra clock cycles at<br/>the end of each command that the SDS bus will<br/>be left at idle.</gap>                        |

| :DIO:SEQuence:GAP?      |                                                    | <gap></gap>             | <gap> returns the currently configured command gap, def:5</gap>                                                                                    |

| :DIO:SEQuence:STATus?   |                                                    | <status></status>       | Returns the current state machine status register (bits 0:3).                                                                                      |

| :DIO:SEQuence:TRIGger      | <seq_id>,<trig_<br>src&gt;, <trig_mode>,<br/><trig_pol>, <trig_<br>dly_en&gt;</trig_<br></trig_pol></trig_mode></trig_<br></seq_id>                                                       |                                                                                                                                     | <seq-id> = 1-4, SDS Sequence Number<br/><trig_src> = refer to footnote in page 9<br/><trig_mode> = &lt;1 0&gt;, 0=edge,1=level<br/><trig_pol> = &lt;1 0&gt;, 0=normal, 1=inverted<br/>(low-truth)<br/><trig_dly_en> = &lt;1 0&gt;, 1=enabled delay,<br/>0 = no delay</trig_dly_en></trig_pol></trig_mode></trig_src></seq-id> |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| :DIO:SEQuence:TRIGger?     | <seq_id></seq_id>                                                                                                                                                                         | <trig_src>,<trig_<br>mode&gt;, <trig_pol>,<br/><trig_dly_en></trig_dly_en></trig_pol></trig_<br></trig_src>                         |                                                                                                                                                                                                                                                                                                                               |

| :DIO <n>:SOURce</n>        | 0-7 or TTLTrg0-7<br>9 or DIO (default)<br>10 or SUBModule1<br>12 or MIPData<br>13 or MIPCIk<br>14 or EXTernal<br>8,11, 15: Reserved                                                       |                                                                                                                                     | <n> = 0-3 DIO pin selection. (PXIe_DIO only)</n>                                                                                                                                                                                                                                                                              |

| :DIO <n>:SOURce?</n>       |                                                                                                                                                                                           | 0-7 or TTLTrg0-7<br>9 or DIO (default)<br>10 or SUBModule1<br>12 or MIPData<br>13 or MIPClk<br>14 or EXTernal<br>8,11, 15: Reserved | <n> = 0-3 DIO pin selection. (PXIe_DIO only)</n>                                                                                                                                                                                                                                                                              |

| :DIO:MIPI:IMMediate:READ?  | <mipi_slave_id>,<br/><half_speed>,<br/><slave_reg_addr></slave_reg_addr></half_speed></mipi_slave_id>                                                                                     | <slave_response, 1<br="">byte&gt;</slave_response,>                                                                                 | Immediately generates MIPI "Write Register" command                                                                                                                                                                                                                                                                           |

| :DIO:MIPI:IMMediate:WRITe  | <mipi_slave_id>,<br/><half_speed>,<br/><slave_reg_addr>,<br/><slave_reg_data></slave_reg_data></slave_reg_addr></half_speed></mipi_slave_id>                                              |                                                                                                                                     | Immediately generates MIPI "READ Register"<br>command                                                                                                                                                                                                                                                                         |

| :DIO:MIPI:IMMediate:ZERO   | <mipi_slave_id>,<br/><slave_reg_data></slave_reg_data></mipi_slave_id>                                                                                                                    |                                                                                                                                     | Immediately generates the protocol specific MIPI "Write Zero Register" command                                                                                                                                                                                                                                                |

| :DIO:MIPI:SEQuence:APPend  | <sds_sequence_<br>ID&gt;, <read_write>,<br/><mipi_slave_id>,<br/><slave_reg_addr>,<br/><slave_reg_data></slave_reg_data></slave_reg_addr></mipi_slave_id></read_write></sds_sequence_<br> |                                                                                                                                     | Appends a single MIPI command to the<br>specified command sequence buffer.<br>SDS_Sequence_ID = 1-4                                                                                                                                                                                                                           |

| :DIO:MIPI:SEQuence:ENABle  | <sds_sequence_<br>ID&gt;, <on off,1 0></on off,1 0></sds_sequence_<br>                                                                                                                    |                                                                                                                                     | Enables specified buffer and configures internal signal routing for MIPI command generation.                                                                                                                                                                                                                                  |

| :DIO:MIPI:SEQuence:ENABle? | <sds_sequence_<br>ID&gt;</sds_sequence_<br>                                                                                                                                               | <0N 0FF,1 0>                                                                                                                        | Returns whether the specified buffer is enabled.                                                                                                                                                                                                                                                                              |

| :DIO:MIPI:SEQuence:HALF    | <1 0>                                                                                                                                                                                     |                                                                                                                                     | Enables/Disables Half-speed clocking during data read.                                                                                                                                                                                                                                                                        |

| :DIO:MIPI:SEQuence:HALF?   |                                                                                                                                                                                           | <1 0>                                                                                                                               |                                                                                                                                                                                                                                                                                                                               |

| :DIO:SSBI:IMMediate:PAIR?  | <read_write>,<br/><pair_id>, <slave_<br>reg_addr&gt;, <slave_<br>reg_data&gt;</slave_<br></slave_<br></pair_id></read_write>                                                              | Read: <slave_<br>response&gt;<br/>Write: &lt;0&gt;</slave_<br>                                                                      | <read_write> = 1 for write, 0 for read<br/><pair_id> = 0 1<br/>Immediately generates SSBI register read/write<br/>command on specified DIO port pairing.</pair_id></read_write>                                                                                                                                               |

| :DIO:SSBI:IMMediate:READ?  | <slave_reg_addr></slave_reg_addr>                                                                                                                    | <slave_response,<br>1 byte&gt;</slave_response,<br> | Immediately generates SSBI "READ Register" command                                                                                                   |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| :DIO:SSBI:IMMediate:WRITe  | <slave_reg_addr>,</slave_reg_addr>                                                                                                                   |                                                     | Immediately generates SSBI "Write Register"                                                                                                          |

|                            | <slave_reg_data></slave_reg_data>                                                                                                                    |                                                     | command                                                                                                                                              |

| :DIO:SSBI:SEQuence:APPend  | <sds_sequence_<br>ID&gt;, <read_write>,<br/><slave_reg_addr>,<br/><slave_reg_data></slave_reg_data></slave_reg_addr></read_write></sds_sequence_<br> |                                                     | Appends a single SSBI command to the specified command sequence buffer.<br>SDS_Sequence_ID = 1-4                                                     |

| :DIO:SSBI:SEQuence:BLOCk?  | <command_count></command_count>                                                                                                                      | <num_responses></num_responses>                     | Executes a previously built sequence of<br>commands and returns the number of read<br>commands executed. Read responses are<br>stored in ScratchPad. |

| :DIO:SSBI:SEQuence:ENABle  | <sds_sequence_<br>ID&gt;, <on off,1 0></on off,1 0></sds_sequence_<br>                                                                               |                                                     | Enables specified buffer and configures internal signal routing for SSBI command generation.                                                         |

| :DIO:SSBI:SEQuence:ENABle? | <sds_sequence_<br>ID&gt;</sds_sequence_<br>                                                                                                          | <0N 0FF,1 0>                                        | Returns whether the specified buffer is enabled.                                                                                                     |

| :DIO:SYNC:CLEAR            |                                                                                                                                                      |                                                     | Clears Sync config and buffers.                                                                                                                      |

| :DIO:SYNC:COERCe           | <on off,1 0></on off,1 0>                                                                                                                            |                                                     | Enables ITG Gap coercion to synchronize<br>SDS:SYNC and waveform play<br>NOTE: Sample clock only:<br>125e6, 62.5e6 & 31.25e6                         |

| :DIO:SYNC:COERCe?          |                                                                                                                                                      | <1 0>                                               |                                                                                                                                                      |

| :DIO:SYNC:ENABle           | <on off,1 0>,<br/><bytes></bytes></on off,1 0>                                                                                                       |                                                     | Configures SDS CMD Buffer 4 and routes<br>outputs of RCV1 and RCV2 to DIO 2/3<br>respectively                                                        |

| :DIO:SYNC:ENABle?          |                                                                                                                                                      | <1 0>                                               | Returns whether a sequence is enabled on SDS CMD buffer 4.                                                                                           |

#### **Triggering Options:**

- "TRIG" = Trigger Even

- "GCOM" = Generation Complete (end of waveform)

- "EXT" = External Input on instrument

- "CONS" = Constant register (manually toggled)

- "TSYN" = Delayed trigger, (i.e., PA Enable delayed trigger)

- "SYNC1" = SYNC1 output/marker

- "SYNC2" = SYNC2 output/marker

"DIO<0-3>" = DIO input pins 0-3

(note: Pins 0 and 1 are used for MIPI, Pins 2 & 3 are used for SSBI,

You will need to use "unused" pins for the protocol you are currently working with)

"TTL<0-7>" = TTL (PXI Backplane triggers 0-7)

# MIPI Command Sequencing Example

#### //DIO Port Init, perform once to set up the communications port:

zbind\_send(ztvsg\_handle,ZT\_TRUE,"outp:dio:reset"); zbind\_send(ztvsg\_handle,ZT\_TRUE,"outp:dio:enab on"); zbind\_send(ztvsg\_handle,ZT\_TRUE,"outp:dio:lev 1.8"); zbind\_send(ztvsg\_handle,ZT\_TRUE,"outp:dio:clock 25e6"); zbind\_send(ztvsg\_handle,ZT\_TRUE,"outp:dio0:sour 13"); // MIPI Clock pin = DIOO zbind\_send(ztvsg\_handle,ZT\_TRUE,"outp:dio1:sour 12"); // MIPI Data pin = DIO1 // Note: you can specify the DIO pins (0-3)

//Perform immediate commands, when needed:

//MIPI immediate Cmd, writes 1 byte to a slave register address:

#### // Params: Slave Addr, Half-speed, RegAddr, Data

zbind\_send(ztvsg\_handle,ZT\_TRUE,"outp:dio:mipi:imm:write %d,0,11,3",slave\_addr);

#### //MIPI Immediate Read:

// Params: Slave Addr, Half-speed, RegAddr

zbind\_send(ztvsg\_handle,ZT\_TRUE,"outp:dio:mipi:imm:read? %d,0,11", slave\_addr);

// Use zbind\_receive to get the return data, 1Byte only:

zbind\_receive(ztvsg\_handle,ZT\_TRUE,"%d",&data);

#### zbind.h information on the zbind\_send() and zbind\_receive() commands:

| /* Fu                         | nction: zbind_send */                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| /* Pu                         | rpose: This function sends a command string to the instrument with */                                                                                                                                                                                                                                                                                                                                                                                                             |

| /*                            | optional locking and string formatting. */                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| /*                            | Parameter 1 is the zbind device handle. */                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| /*                            | Parameter 2 is the lock state. ZT_TRUE will lock subsequent */                                                                                                                                                                                                                                                                                                                                                                                                                    |

| /*                            | commands until a zbind_receive or zbind_releaselock occurs. */                                                                                                                                                                                                                                                                                                                                                                                                                    |

| /*                            | Parameter 3 is the format string. This should be in standard */                                                                                                                                                                                                                                                                                                                                                                                                                   |

| /*                            | formatting, using string conversion specifications. */                                                                                                                                                                                                                                                                                                                                                                                                                            |

| /*                            | The format string defines whether additional parameters are used. */                                                                                                                                                                                                                                                                                                                                                                                                              |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ZT_E                          | RROR _ZBIND_FUNC zbind_send (ZT_HANDLE dev, ZT_BOOL lock, s8 format_str[],);                                                                                                                                                                                                                                                                                                                                                                                                      |

| ZT_E<br>/*==:                 | ***************************************                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| <b>ZT_E</b><br>/*===<br>/* Fu | RROR _ZBIND_FUNC zbind_send (ZT_HANDLE dev, ZT_BOOL lock, s8 format_str[],);                                                                                                                                                                                                                                                                                                                                                                                                      |

| <b>ZT_E</b><br>/*===<br>/* Fu | RROR _ZBIND_FUNC zbind_send (ZT_HANDLE dev, ZT_BOOL lock, s8 format_str[],);<br>*<br>nction: zbind_receive */                                                                                                                                                                                                                                                                                                                                                                     |

| <b>ZT_E</b><br>/*===<br>/* Fu | RROR _ZBIND_FUNC zbind_send (ZT_HANDLE dev, ZT_BOOL lock, s8 format_str[],);   nction: zbind_receive */   rpose: This function returns a response string from the instrument */                                                                                                                                                                                                                                                                                                   |

| 2T_E<br>'*===<br>'* Fu        | RROR _ZBIND_FUNC zbind_send (ZT_HANDLE dev, ZT_BOOL lock, s8 format_str[],);   nction: zbind_receive */   rpose: This function returns a response string from the instrument */   with optional locking and string formatting. */                                                                                                                                                                                                                                                 |

| <b>2T_E</b><br>*===<br>* Fu   | RROR _ZBIND_FUNC zbind_send (ZT_HANDLE dev, ZT_BOOL lock, s8 format_str[],);   nction: zbind_receive */   rpose: This function returns a response string from the instrument */   with optional locking and string formatting. */   Parameter 1 is the zbind device handle. */                                                                                                                                                                                                    |

| 2T_E<br>'*===<br>'* Fu        | RROR _ZBIND_FUNC zbind_send (ZT_HANDLE dev, ZT_BOOL lock, s8 format_str[],);   nction: zbind_receive */   rpose: This function returns a response string from the instrument */   with optional locking and string formatting. */   Parameter 1 is the zbind device handle. */   Parameter 2 is the lock state. ZT_TRUE will unlock a current */                                                                                                                                  |

| ZT_E<br>/*===<br>/* Fu        | RROR _ZBIND_FUNC zbind_send (ZT_HANDLE dev, ZT_BOOL lock, s8 format_str[],);   nction: zbind_receive */   rpose: This function returns a response string from the instrument */   with optional locking and string formatting. */   Parameter 1 is the zbind device handle. */   Parameter 2 is the lock state. ZT_TRUE will unlock a current */   lock, ZT_FALSE will only call the instrument if it is not */                                                                   |

| ZT_E<br>/*===<br>/* Fu        | RROR _ZBIND_FUNC zbind_send (ZT_HANDLE dev, ZT_BOOL lock, s8 format_str[],);   nction: zbind_receive */   rpose: This function returns a response string from the instrument */   with optional locking and string formatting. */   Parameter 1 is the zbind device handle. */   Parameter 2 is the lock state. ZT_TRUE will unlock a current */   lock, ZT_FALSE will only call the instrument if it is not */   currently locked. */                                            |

| ZT_E<br>/*===<br>/* Fu        | RROR _ZBIND_FUNC zbind_send (ZT_HANDLE dev, ZT_BOOL lock, s8 format_str[],);   nction: zbind_receive */   rpose: This function returns a response string from the instrument */   with optional locking and string formatting. */   Parameter 1 is the zbind device handle. */   Parameter 2 is the lock state. ZT_TRUE will unlock a current */   lock, ZT_FALSE will only call the instrument if it is not */   Parameter 3 is the format string. This should be in standard */ |

ZT\_ERROR \_ZBIND\_FUNC zbind\_receive (ZT\_HANDLE dev, ZT\_BOOL unlock, s8 format\_str[], ...);

#### Copyright © 2017 LitePoint, A Teradyne Company.

All rights reserved

#### RESTRICTED RIGHTS LEGEND

No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, without the prior written permission of LitePoint Corporation.

#### DISCLAIMER

LitePoint Corporation makes no representations or warranties with respect to the contents of this manual or of the associated LitePoint Corporation products, and specifically disclaims any implied warranties of merchantability or fitness for any particular purpose. LitePoint Corporation shall under no circumstances be liable for incidental or consequential damages or related expenses resulting from the use of this product, even if it has been notified of the possibility of such damages.

If you find errors or problems with this documentation, please notify LitePoint Corporation at the address listed below. LitePoint Corporation does not guarantee that this document is errorfree. LitePoint Corporation reserves the right to make changes in specifications and other information contained in this document without prior notice.

#### TRADEMARKS

LitePoint and the LitePoint logo are registered trademarks of LitePoint Corporation. z8751 is a trademark of LitePoint Corporation. All other trademarks or registered trademarks are owned by their respective owners.

CONTACT INFORMATION LitePoint Corporation 575 Maude Court

5/5 Maude Court Sunnyvale, CA 94085-2803 United States of America

+1.866.363.1911 +1.408.456.5000

LITEPOINT TECHNICAL SUPPORT www.litepoint.com/support

Doc: 1075-0078-001 July 2017 Rev 2